Entité: AMPERE - UMR 5005

**Adresse**: Lyon/Villeurbanne

Contact: herve.morel@insa-lyon.fr

# Les Rendez-vous Flabilite du CFF Mardi 5 janvier 2021

#### **Body-diode conduction and MOSFET oxide degradation**

Hervé Morel, Directeur de Recherche, CNRS, Ampère

#### **Contexte**

FUI/SEFORA (2008-2012), SiC-JFET, Diode-less inverters ...

Projet IA/GENOME/PREMICE (2012 → 2017) (SAFRAN, Ampère, SATIE ...)

Évaluation de la robustesse et analyse des modes de défaillance des composants grands gap

**Cheng Chen**, Studies of SiC power devices potential in power electronics for avionic applications. Thèse de doctorat, soutenue le 04-11-2016 à l'Université Paris-Saclay, sous la direction de S. Lefebvre et de H. Morel.

**Oriol Aviñó Salvadó**, Contribution to the Study of the SiC MOSFET Gate Oxide, PhD Dissertation, 14/12/2018, INSA Lyon Supervisor : H. Morel, C. Buttay

#### **Contexte 2**

**Quentin MOLIN**, Contribution à l'étude de la robustesse des MOSFET-SiC haute tension : dérive de la tension de seuil et tenue aux courts-circuits, Thèse de doctorat, 14/12/2018, INSA Lyon

... SiCRET, IRT St Exupéry

## Tester la diode interne ?

Pour des applications « diode-less inverter »

- Réduire le nombre de composants

- Améliorer la fiabilité

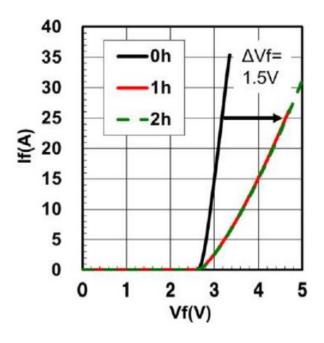

- Risque de Stacking Faults (V<sub>ON</sub> ↑)

- Risque de dégradation de la résistance de source (FUI/SEFORA, SiC-JFET)

Tester la conduction de la diode interne

KUSUMOTO, Osamu, OHOKA, Atsushi, HORIKAWA, Nobuyuki, et al. Reliability of diode-integrated SiC power MOSFET (DioMOS). Microelectronics Reliability, 2016, vol. 58, p. 158-163.

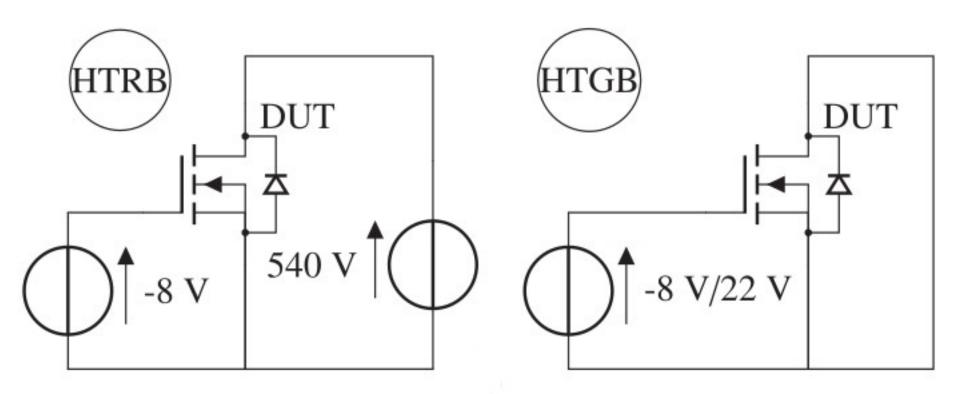

#### **Test standards**

#### **JEDEC STANDARD JESD22-A108D**

Maximum temperature (Specification)

Projet IA/GENOME PREMICE (2012 → 2017)

SALVADÓ, Oriol Aviñó. Contribution to the study of the SiC MOSFETs gate oxide. Thèse de doctorat, INSA Lyon, 2018.

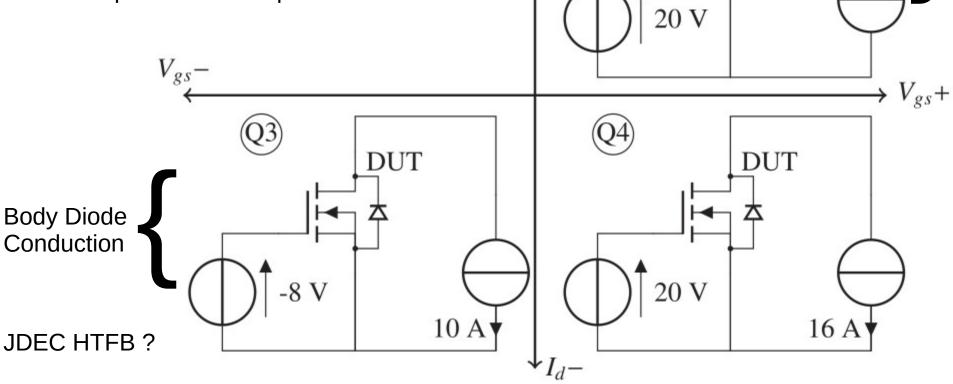

16 A

DUT

Channel

Conduction

# **Body Diode Conduction Test**

$I_d$ +

SALVADÓ, Oriol Aviñó. Contribution to the study of the SiC MOSFETs gate oxide. Thèse de doctorat, INSA Lyon, 2018.

Même puissance dissipée ≈ 37.3 W

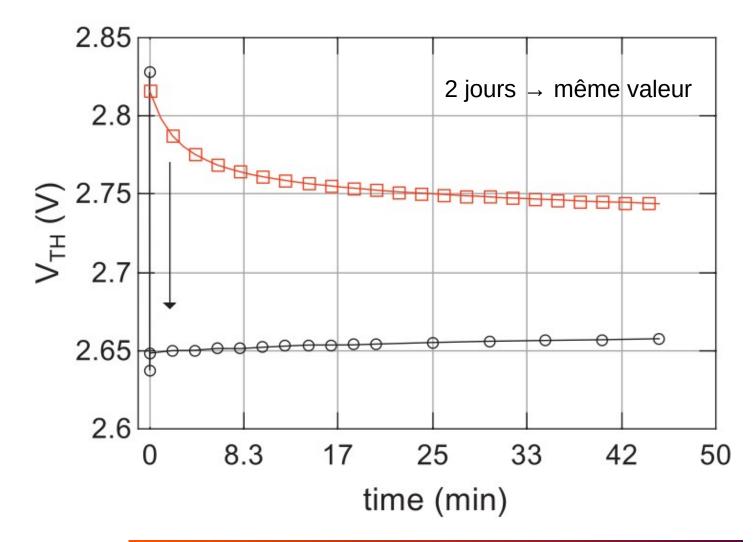

# Mesurer V<sub>TH</sub>

#### **V**<sub>TH</sub> protocole

MOLIN, Quentin, KANOUN, Mehdi, RAYNAUD, Christophe, et al. Measurement and analysis of SiC-MOSFET threshold voltage shift. Microelectronics Reliability, 2018, vol. 88, p. 656-660.

Quentin MOLIN, Contribution à l'étude de la robustesse des MOSFET-SiC haute tension : dérive de la tension de seuil et tenue aux courts-circuits, Thèse de doctorat, 14/12/2018, INSA Lyon

Protocole avec préconditionnement, Sujet de discussion ...

- 1. Negative bias of -8 V during 1 s is applied.

- 2. Threshold voltage is measured (JEDEC/Datasheet).

# **Body Diode Conduction Test**

Wolfspeed C2M008012D MOSFET

Température de canal estimée ≈ 150 °C

Calibration  $R_{DS}^{ON}(T_c)$

**Mesure** de  $V_{TH}(t)$  (protocole)

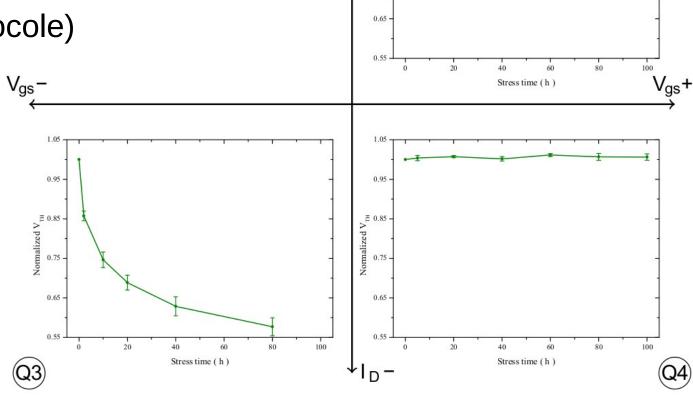

Comportement anormal dans Q3!

**BDCT**

<sub>1</sub> Λ Γ Β +

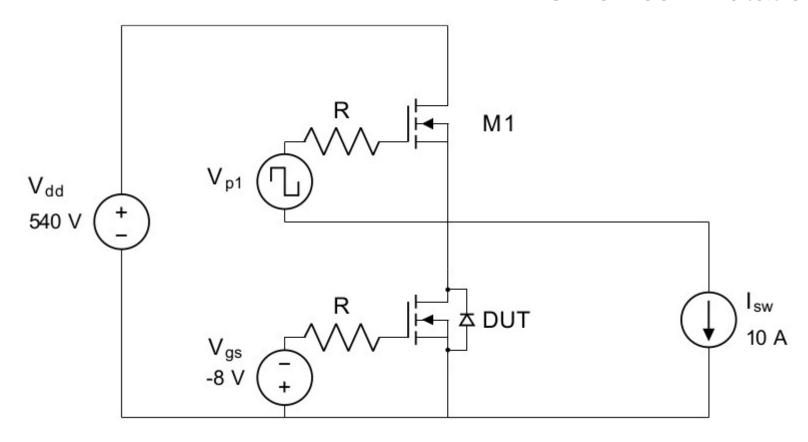

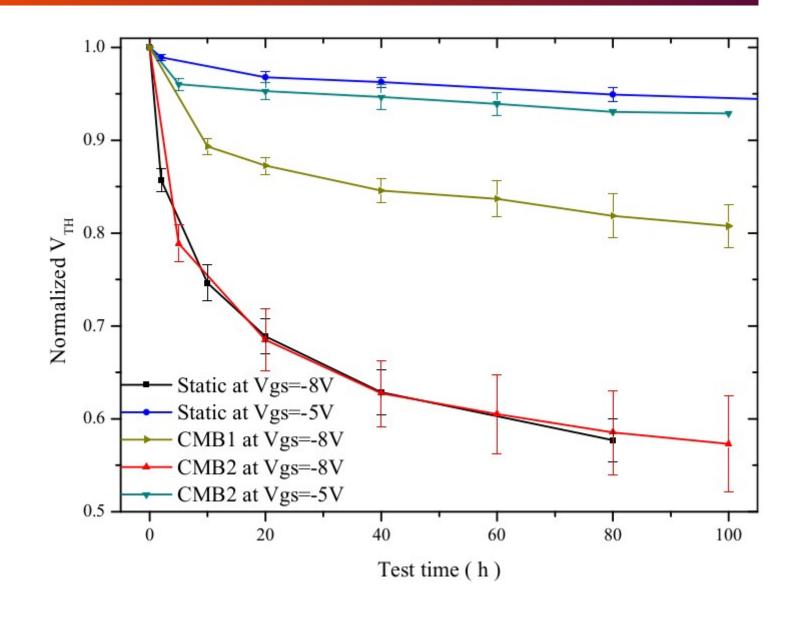

# **Chopper Mode Bias (CMB)**

#### **BDCT** en commutation!

Motivation: la commutation peut favoriser l'injection de porteurs (chauds) dans l'oxyde.

Structure :back to back Test-bench plus difficile à mettre au point

# **CMB**: autoperturbations!

CEM : Autoperturbation du DUT (qui ne commute pas) par M1  $\rightarrow$  pics sur le  $V_{GS}$  (Miller)

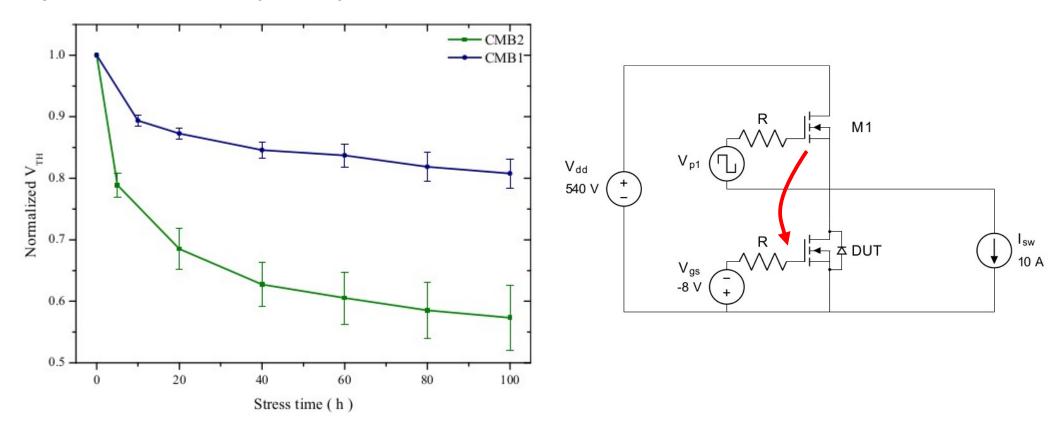

CMB1 → CMB2 (~ 6 mois) → dégradations aggravées !

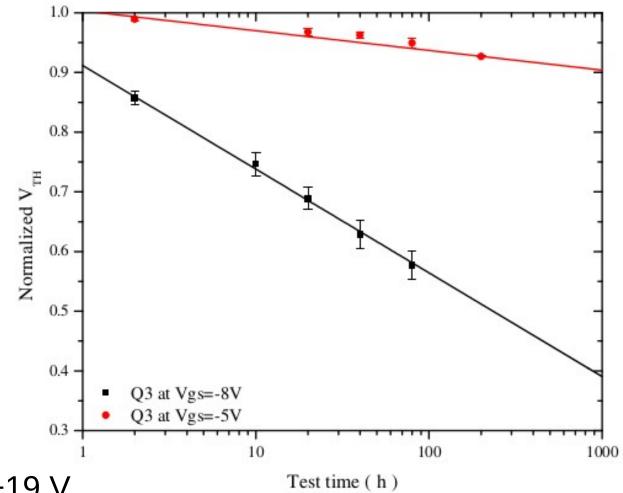

#### CMB: rôle de VGG-

Forte influence!

#### **Wolfspeed datasheet**

C3M0075120J

Rev. B, 07-2019

« Note (1): When using MOSFET Body Diode

V<sub>GSmax</sub> = -4 V/+19 V »

Initialement,  $V_{GSmax} = -8 \text{ V}/+19 \text{ V}$

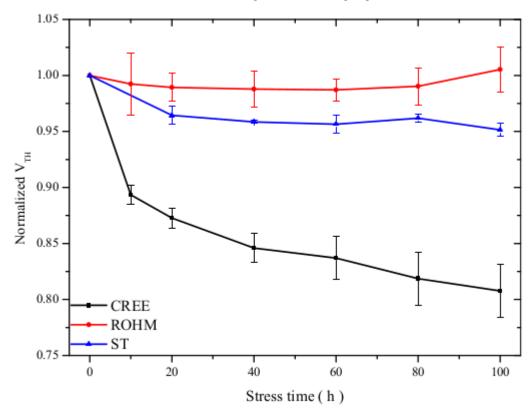

### Influence du fabricant

Comparaison de la dérive CMB (BDCT) pour différents fabricants

Technologie de fabrication de l'oxyde de grille ...

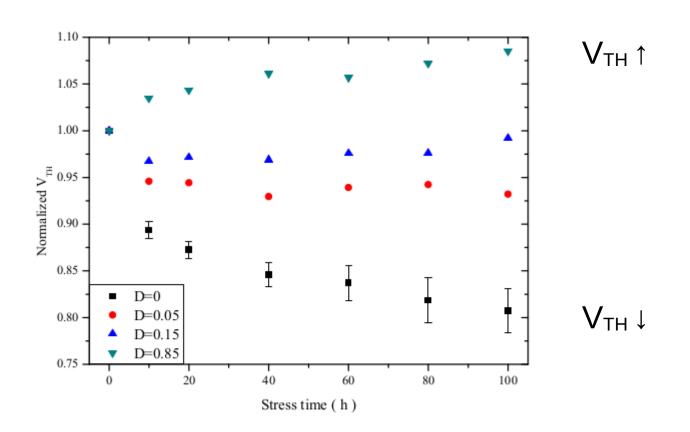

# Rôle du rapport cyclique

Rôle du rapport cyclique (conduction inverse canal ou body diode) ... et la vraie vie ? ... SiCRET → ITASC

### CMB/BDCT

La commutation influe assez peu!

CMB → BDCT!

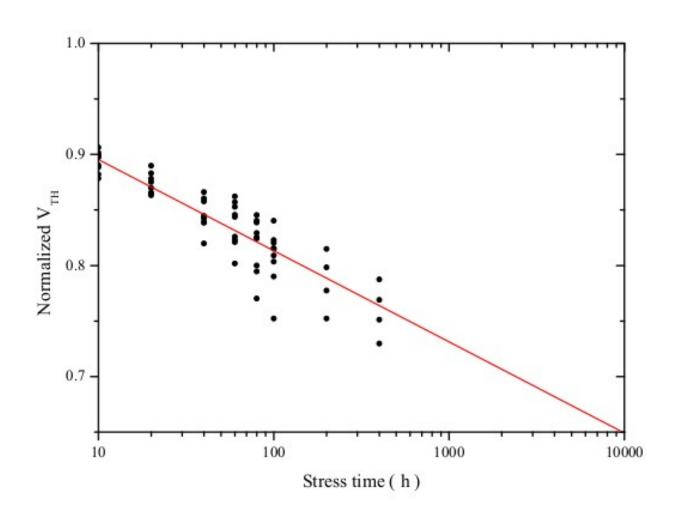

# Extrapolation à long terme

Jusqu'à 35 % sur  $V_{TH}$  à 10<sup>4</sup> h ... mais le composant fonctionne toujours ! (immunité  $\uparrow$  , risque de courts-circuits  $\uparrow$ )

# Interprétation ...

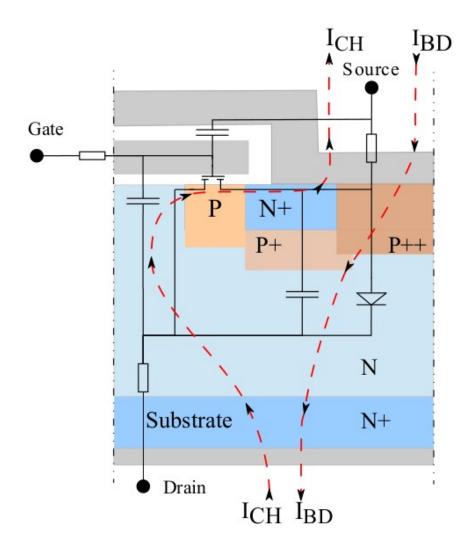

BDCT (CMB) → I<sub>BD</sub> important

$I_{CH} \rightarrow pas$  d'influence sur la dérive de  $V_{TH}$ !

Lieux différents! BDCT ≠ HTGB<sup>-</sup>!!!

... to be continued!

#### **Conclusions**

Pas de dégradation de stacking faults observée!

- Légère dégradation de la résistance de source (métallisation)

- Forte diminution de  $V_{TH}$  en BDCT (Wolfspeed) mais toujours fonctionnel.

- To be continued ...

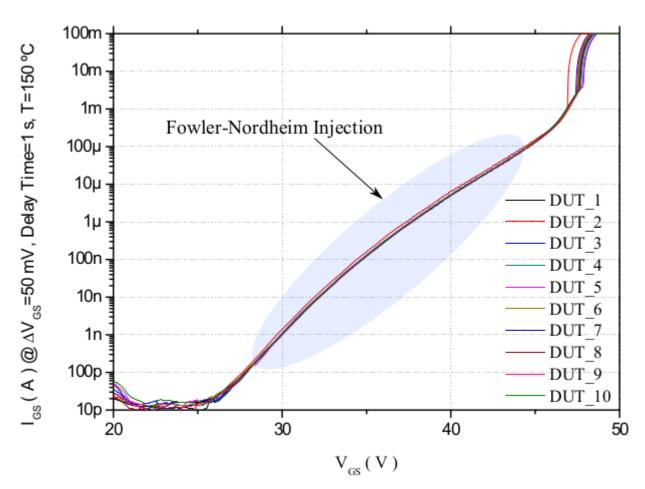

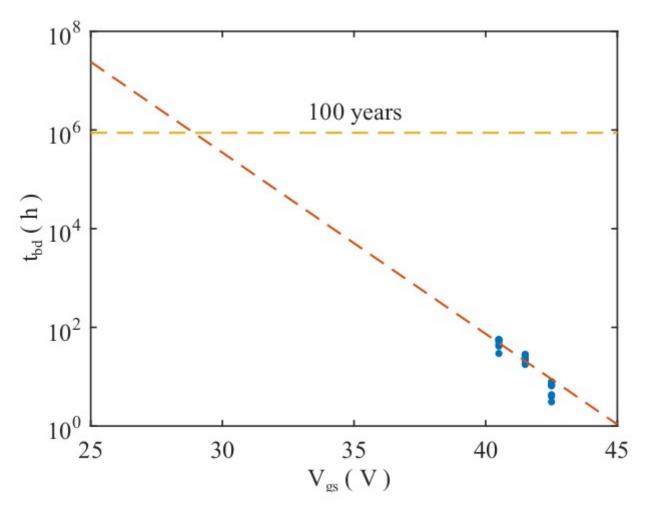

## TDDB (real life)

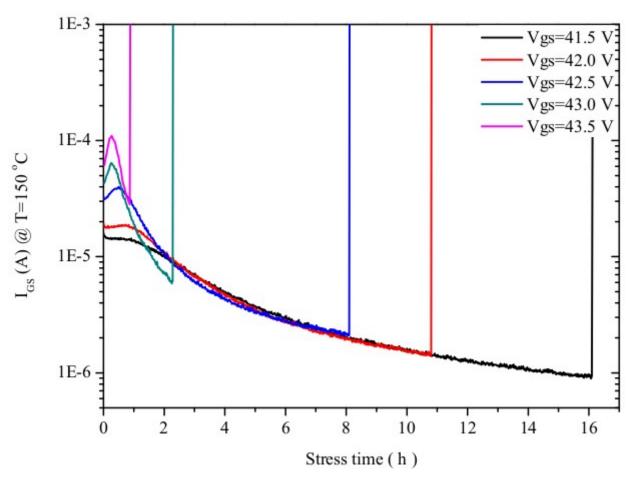

Différents régimes : 1- pas de courant, 2- FN, 3- dégradation rapide

# **TDDB** (Switching)

Pas d'influence significative de la commutation!

#### **TDDB: courant transitoire**

Similitudes avec les courants (transitoires) dans la grille pendant les courts-circuits !

To be continued ...