# FITAGAN

# Flabilité des TrAnsistors GaN de moyenne puissance pour applications automobiles

- Moncef KADI → IRSEEM EA 4353 ESIGELEC

- Pascal DHERBECOURT→ GPM UMR CNRS 6634 Université de Rouen Normandie

# LES RENDEZ-VOUS FIABILITE DU CFF

05/01/2021

# Contexte global (1): Fiabilité de l'électronique embarquée dans les véhicules électriques

- > Le véhicule électrique :

- Des objectifs communs:

- ✓ Moins de CO2 et de gaz toxiques émis

- Différentes déclinaisons:

- ✓ Tout électrique (EV)

- ✓ Hybride rechargeable sur réseau (PHEV)

- ✓ Hybride complet (FHEV)

- ✓ <u>Hybridation légère (MHEV)</u>

- ✓ Start & Stop

- Compromis coût/réduction des émissions : MHEV

- Coût: compatible réseau de bord 48V

- Emissions: -7 à 12%

Mercedes-Benz

La technologie MHEV est proposée actuellement dans des modèles de véhicules par plusieurs constructeurs

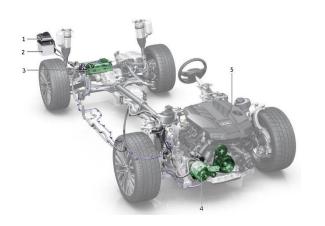

# Contexte global (2): En quoi consiste cette hybridation MHEV dite légère?

Source: Valeo Hybrid4All 48V MHEV system components

1.Powertrain Control Unit (PCU)

2.14V battery sensor

3.Belt Starter Generator (BSG) 8 - 12 kW / 55

Nm Peak, with integrated inverter

4.DC/DC converter, 60 V / 12 V, 2 kW

5.48V battery, 200 - 600 kJ

#### Source: Audi A8 48V MHEV

1.DC/DC converter

2.low voltage battery (12 V)

3.high voltage battery (48 V)

4.48V belt-drive starter-generator

5.3.0 TFSI internal combustion engine

#### Source: Continental 48V MHEV system components

1.electric machine with integrated inverter 2.DC/DC converter (48 V / 12 V)

# Contexte FITAGAN: Fiabilité des transistors de puissance en technologie GaN pour convertisseurs DC/DC

- ✓ Besoin de convertisseurs plus efficaces et moins encombrants

- ✓ Le silicium (Si) atteint ses limites de par ses propriétés physiques

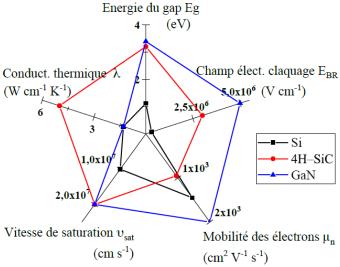

- ✓ GaN et SiC : nouvelles technologies (température maximale d'opération accrue, faible résistance à l'état passant  $R_{DSON}$ , la tension de claquage et la vitesse de commutation accrues)

- ✓ La fréquence d'opération plus élevée permet de réduire la taille des composants passifs, en particulier les inductances

Source : Convertisseur de courant 12-48V DC/DC de Valeo

# Contexte FITAGAN: Fiabilité des transistors de puissance en technologie GaN pour convertisseurs DC/DC

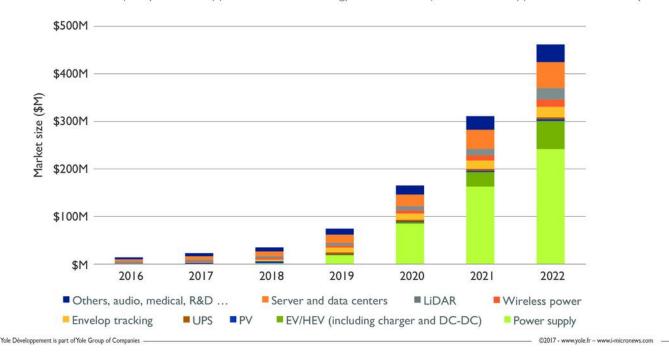

### GaN power device market size split by application (\$M)

(Source: Power GaN 2017: Epitaxy, Devices, Applications, and Technology Trends 2017 report, Yole Développement, October 2017)

#### OBJECTIFS FITAGAN

#### Etudier la fiabilité des transistors GaN moyenne tension (100V)

- Déterminer leur principaux mécanismes de défaillances

- o Identifier les indicateurs de défaillances

- Déterminer les seuils critiques des dégradations des paramètres électriques à partir desquels il y a défaillance

Jian-Zhi FU, « Mise en œuvre de moyens de vieillissement accéléré et d'analyses dédiés aux composants de puissance grand gap » Thèse de doctorat de l'université de Rouen Normandie, Décembre 2018.

### Elaborer un système de surveillance des paramètres du convertisseur DC/DC in-situ

- Comment insérer des éléments de surveillance sans modifier les performances intrinsèques du convertisseur?

- Etudier la possibilité de contrôle de certains indicateurs pendant une phase d'arrêt (courant de fuite)?

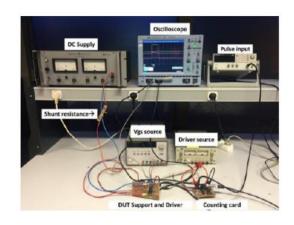

# Compétences techniques et bancs associés:

Caractérisation électrique (banc GPM)

Caractérisation physique (équipements du GPM )

Caractérisation capacitive (banc IRSEEM)

Stress en CC (banc IRSEEM)

## Technologie des transistors GaN

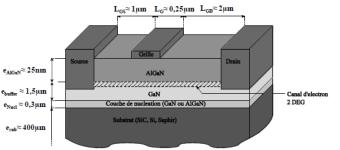

□ HEMT AlGaN/GaN : Création d'un canal de conduction 2 DEG à

l'interface AlGaN/GaN

Structure nativement Normally-ON

M. Avcu, "Caractérisation des effets parasites dans les HEMTs GaN : développement d'un banc de mesure  $3\omega$ ", thèse de doctorat, Université de Limoges, 2014.

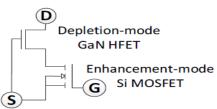

### □ Différentes technologies pour réaliser des GaN Normally-OFF:

en jouant sur le contact de grille

G

p-GaN

S AlGaN barrier

GaN channel

buffer

Si or SiC substrate

Principe du GaN cascode [\*]

Structure du e HEMT GaN [\*\*]

[\*] E.Jones, D.Costinett; "Review of Commercial GaN Power Devices ans GaN-Based Design Challenges", 2014 IEEE Workshop on Wide-bandgap Power Devices and Applications (WiPDA), Knoxville, USA, October 2014.

[\*\*] M.Meneghini & al; "Technology and Reliability of Normally-Off GaN HEMTs with p-Type Gate", Energies, Vol 10, February 2017.

# Différentes phases du projet : 18 mois

- 1. Étude bibliographique et choix du composant d'étude GaN de découpe

- a) Offre commerciale, concertation avec les partenaires

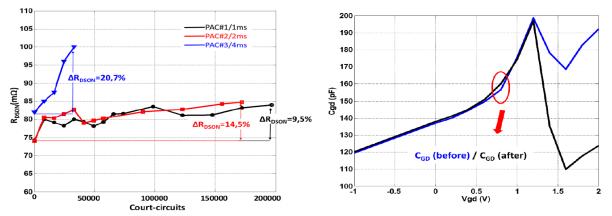

- Caractérisation et vieillissement du DUT en mode CC

- a) Expertise des équipes de l'IRSEEM et du GPM dans la caractérisation et les bancs de stress en CC de ce type de composant

- b) Développement d'un banc de vieillissement, de bancs de caractérisations électriques

- c) Analyse et recherche des modes de défaillance

- 3. Design du convertisseur DC/DC

- a) Conception et réalisation d'un démonstrateur

- Design et simulation d'un convertisseur avec « Health Monitoring » pour convertisseur DC/DC

- a) Poursuive la collaboration auprès d'industriels (Valéo)

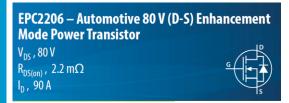

## Composant GaN retenu pour l'étude

| Paramètre (symbole)                        | Valeur (conditions)                                                  |

|--------------------------------------------|----------------------------------------------------------------------|

| Continuous Drain current (ID)              | 90 A (Tc=25 °C)                                                      |

| Gate-Source Voltage (VGS)                  | -4 V +6 V                                                            |

| Drain -Source Breakdown Voltage (V(BR)DSS) | 80 V (Vgs=0 V, Id=100 uA)                                            |

| Drain-Source On Resistance                 | $1.8 \text{ m}\Omega \text{ (VGS} = 5 \text{ V, ID} = 29 \text{ A)}$ |

| Gate Threshold Voltage (VGS(TH))           | 1.2 V (VDS=VGS, ID=13 mA)                                            |

#### Avantages:

- Faible R<sub>DS(ON)</sub>

- Tension compatible avec l'application recherchée

- Fort courant à l'état passant

- Boitier compact (faibles éléments parasites)

#### Inconvénients :

- Accès difficiles au composant (Grille, Drain et Source)

- Difficultés de contact reproductibles lors du report

- Structure physique interne complexe

EPC2206

Die Size: 6.05 mm x 2.3 mm

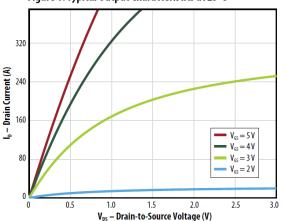

Figure 1: Typical Output Characteristics at 25°C

#### Demo Board

Front view

#### **DESCRIPTION**

The EPC90122 development board is a 80 V maximum device voltage, 40 A maximum output half bridge current, with onboard gate drives, featuring the **EPC2206** enhancement mode (eGaN) field effect transistor (FET).

### 80 V Half-bridge with Gate Drive, Using EPC2206

| Paramètre (symbole)           | Valeur                    |

|-------------------------------|---------------------------|

| Gate Drive Input Supply (VDD) | 7V à 12V                  |

| Bus Input Voltage (VIN)       | 64V                       |

| Output Current (Iout)         | 40A                       |

| PWM Logic Input Voltage       | Input 'Low' : de 0 à 1.5V |

| (VPWM)                        | Input 'High': de 3.5 à 6V |

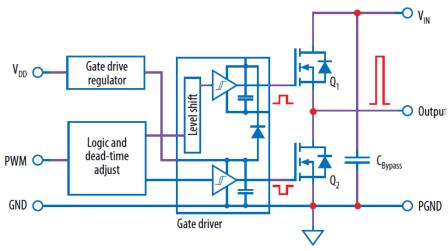

#### LMG1205 80-V, 1.2-A to 5-A, Half Bridge GaN Driver

Figure 1: Block diagram of EPC90122 development board

# Simulation SPICE du composant et d'un schéma de convertisseur (demo board)

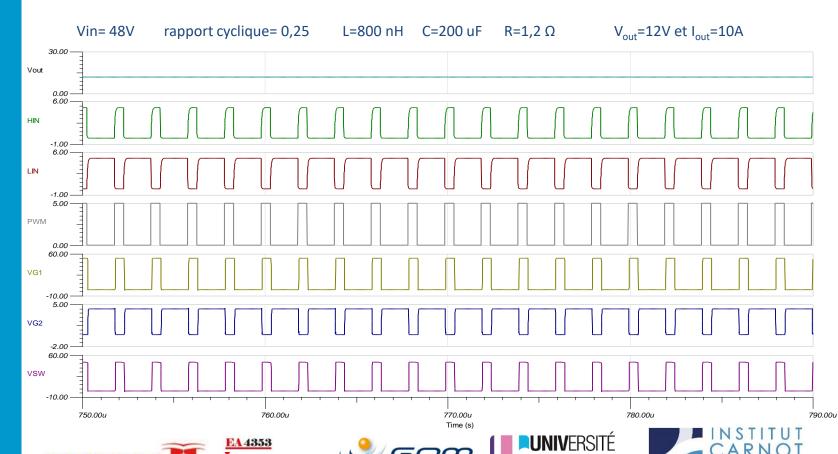

# Simulation SPICE du composant et d'un schéma de convertisseur (demo board)

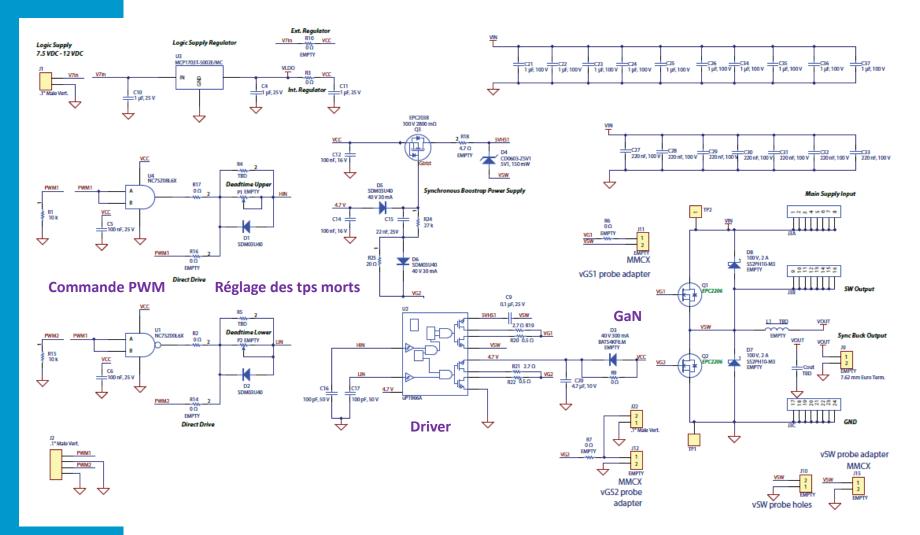

Simulation du schéma électrique du circuit EPC90122 sur TINA

#### Formes d'ondes d'entrée et de sortie du circuit EPC90122

# Mesures préliminaires du convertisseur (demo board)

- Mesures du circuit EPC90122

- ✓ Ajout d'un filtre en sortie avec possibilité de considérer plusieurs charges (courant entre 0,25A et 10A)

- ✓ Deux potentiomètres pour régler le temps mort

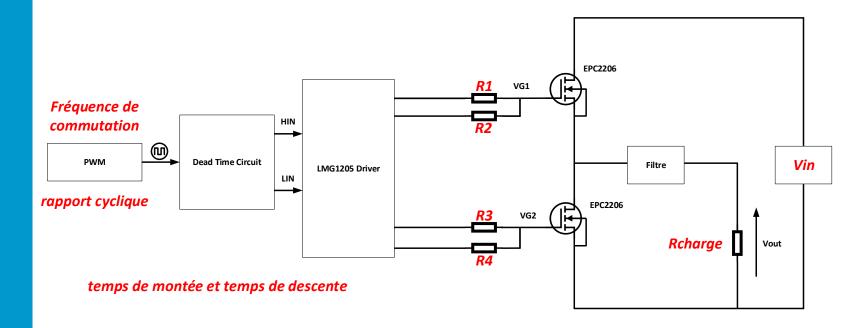

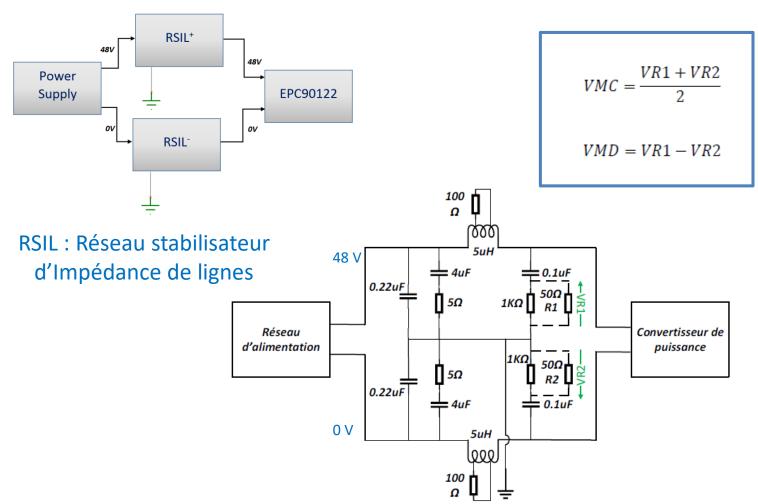

- Paramètres influents sur la CEM

- ✓ Plusieurs paramètres peuvent modifier la réponse spectrale (signature CEM du convertisseur)

Schéma de principe d'une simulation CEM

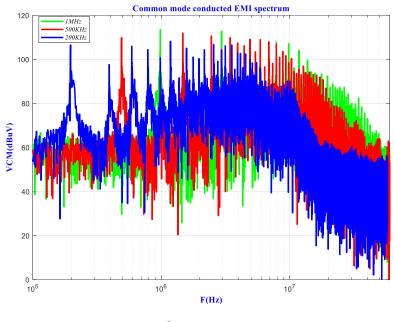

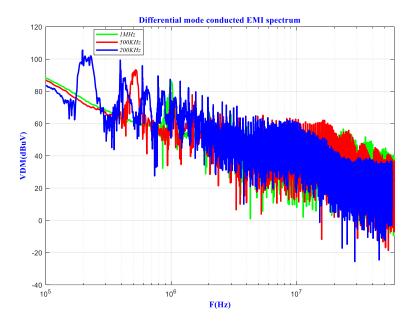

Effet de la montée des fréquences de commutation

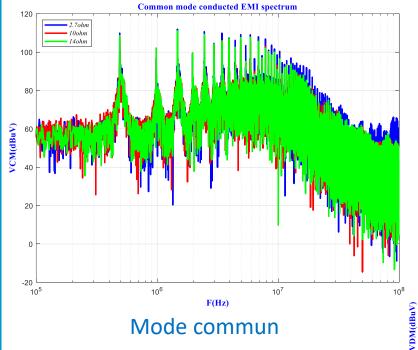

#### Mode commun

#### Mode différentiel

Effet de l'augmentation du produit RC à l'entrée des grilles des transistors

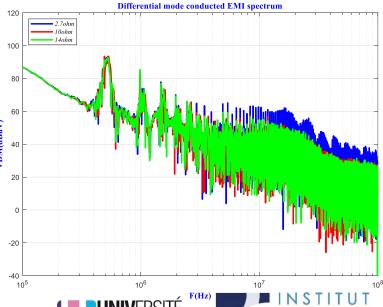

#### Mode différentiel

## **Etat d'avancement et perspectives**

#### ☐ Etat d'avancement:

- Réalisation d'un dispositif de report du composant pour les phases de caractérisations :

- Méthode simple avec une réalisation en interne

- Reproductibilité de la qualité de contact → Influence sur les mesures

- Réalisation d'une carte de stress en court-circuit avec contrôle du courant

- Premiers essais en cours

- Test de la demo board

- Problème de surtensions en sortie (overshoot)

- Conception et routage d'un convertisseur de démonstration

#### Perspectives

- Analyse des principaux indicateurs de défaillances

- Concevoir et réaliser un démonstrateur intégrant le contrôle des principaux indicateurs de défaillance in-situ

- Etablir un guide méthodologique à destination des industriels (sous réserve de respecter la confidentialité)

## **Etat d'avancement et perspectives**

#### ✓ Valorisation scientifique et en direction des industriels :

- Poursuivre la montée en compétence sur la fiabilité des GaN et accroitre le rayonnement des acteurs du projet et de l'Institut CARNOT-ESP

- Présentation de ces travaux dans des conférences spécialisées (ESREF 2021 et IRPS 2021) et publications dans des journaux spécialisés

- Consolider la collaboration initiée avec Valéo

# Merci de votre attention Questions ?